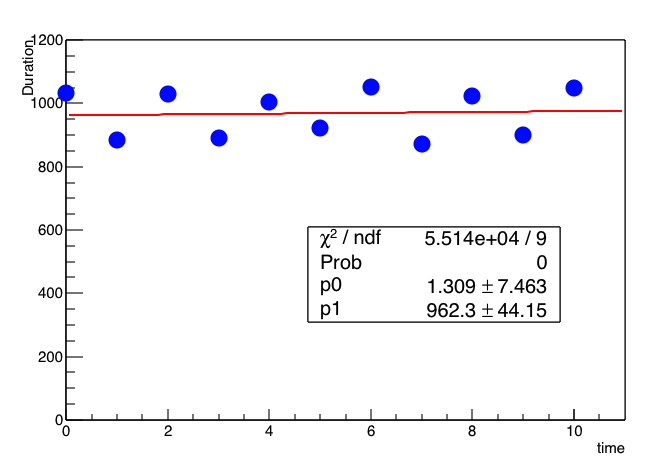

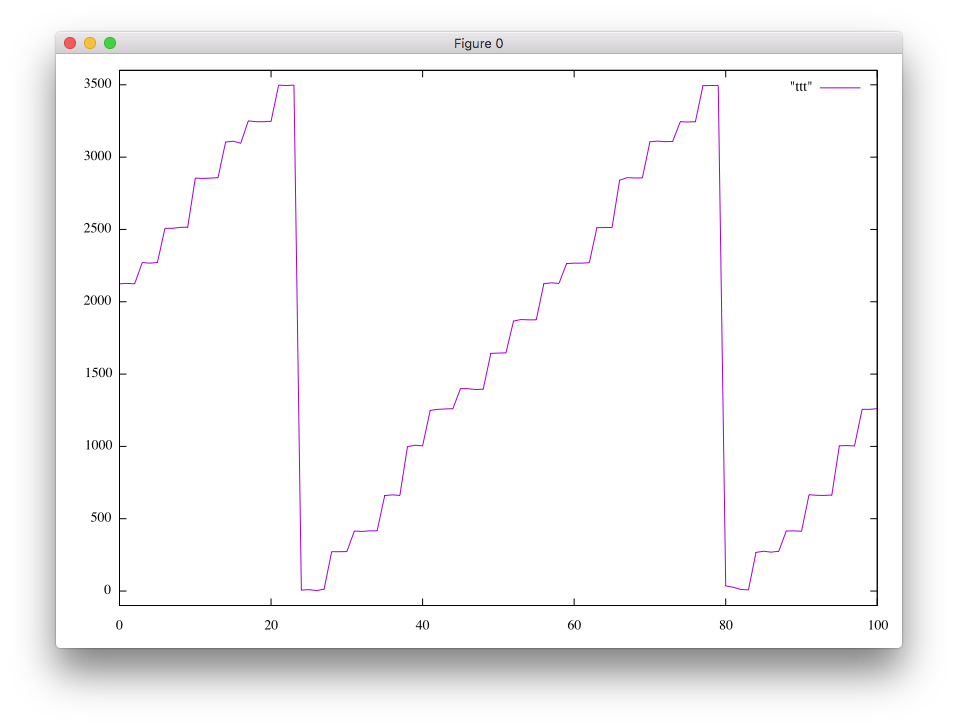

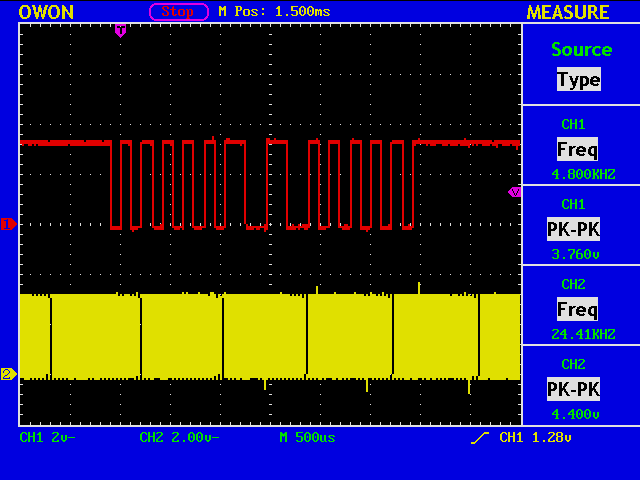

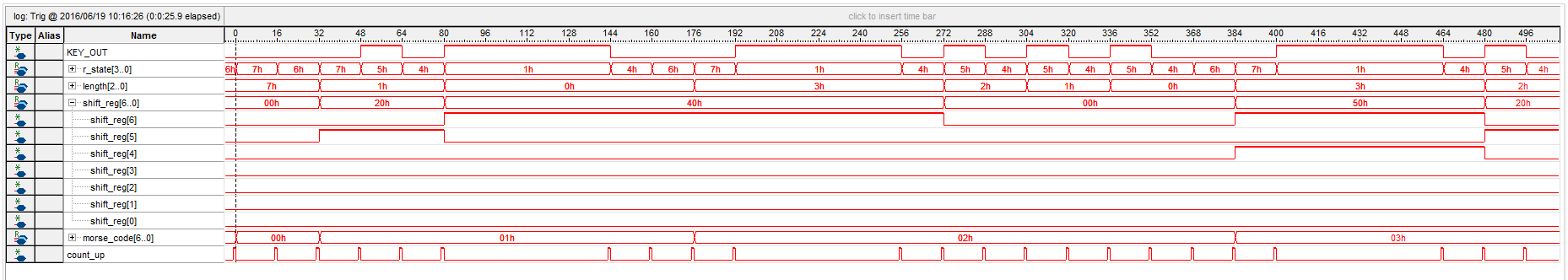

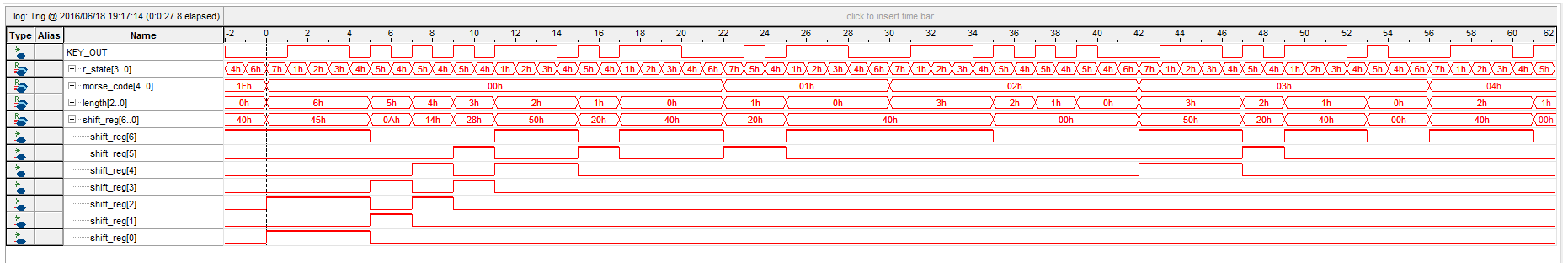

I thought that the dot duration may change in time, but we need more observations to say anything.

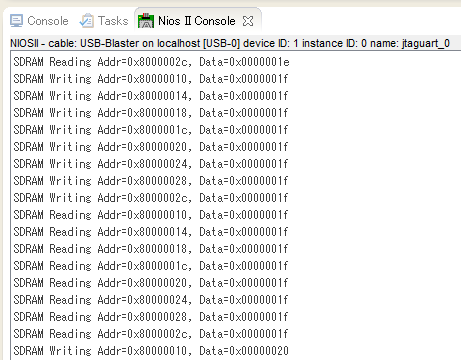

// file name = mytest.cc

{

TCanvas *c = new TCanvas( "test" );

TH1 *frame = c->DrawFrame( 0.0, 0.0, 11.0, 1200.0 );

frame->GetXaxis()->SetTitle("time");

frame->GetYaxis()->SetTitle("Duration");

double x[11] = { 0.0, 1.0, 2.0, 3.0, 4.0, 5.0, 6.0, 7.0, 8.0, 9.0, 10.0 };

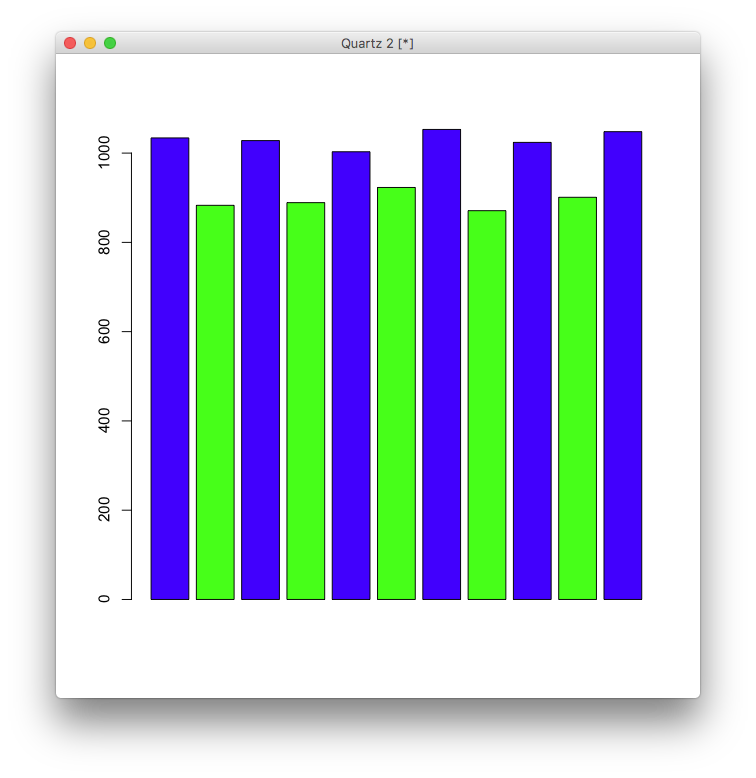

double y[11] = { 1034, 883, 1028, 889, 1003, 923, 1053, 871, 1024, 901, 1048};

TGraph *g = new TGraph( 11, x, y );

g->SetMarkerStyle( 20 );

g->SetMarkerColor( 4 );

g->SetMarkerSize ( 2 );

g->Draw( "P" );

TF1 *f1 = new TF1( "f1", "[0]*x+[1]" );

gStyle -> SetOptFit(1111);

g->Fit (f1);

}

% root -x mytest.cc ------------------------------------------------------------------------- | Welcome to ROOT 6.06/08 http://root.cern.ch | | (c) 1995-2016, The ROOT Team | | Built for macosx64 | | From heads/v6-06-00-patches@v6-06-06-30-g3bae07b, Sep 01 2016, 14:28:05 | | Try '.help', '.demo', '.license', '.credits', '.quit'/'.q' | ------------------------------------------------------------------------- root [0] Processing mytest.cc... **************************************** Minimizer is Minuit / Migrad Chi2 = 55135.1 NDf = 9 Edm = 2.85319e-19 NCalls = 32 p0 = 1.30909 +/- 7.46271 p1 = 962.273 +/- 44.15 root [1]