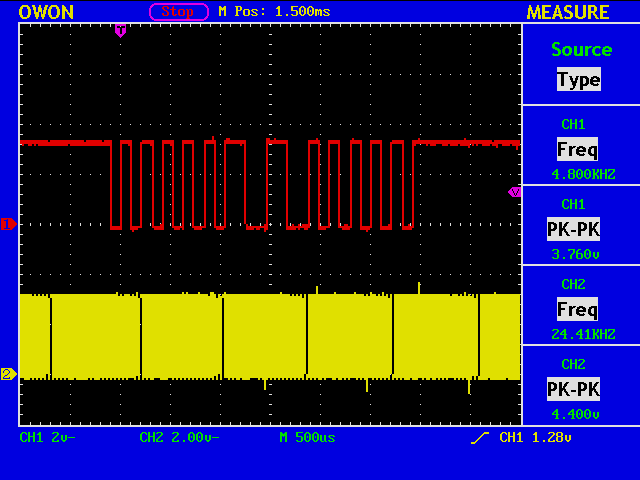

今、6個の短点を送出しています。赤色のトレースは、短点の接点から得られた信号で、黄色のトレースは、FPGA内の簡単なデバウンス回路からのものです。

同じデバイスの中に、マークとスペースの長さを測定する回路を含ませることは容易です。

上の図に含まれる数値を読み取れば、あなたはRの短いスクリプトを書くことができます。

% R > dat_v=c(1034, 883, 1028, 889, 1003, 923, 1053, 871, 1024, 901, 1048) > barplot(dat_v, col=c("blue", "green"))

青色の棒はマーク(low)の長さに、緑色の棒はスペース(high)の長さに対応します。あなたは、マークとスペースとの比が1.0ではなく、さらなる調整が必要であることに、直ちに気が付きます。